Samsung Accelerates AI Infrastructure With Early HBM4 Mass Production

The global race to build ever more powerful AI infrastructure has reached another inflection point. Samsung Electronics has confirmed it has begun mass production of its High Bandwidth Memory 4, or HBM4, and has already shipped commercial volumes to customers. In a market where timing is everything and capacity constraints can stall billion pound datacentre projects, that early move carries significant implications for the wider construction, infrastructure and industrial technology ecosystem.

HBM4 is not just another memory upgrade. It is a foundational component in the AI hardware stack that underpins hyperscale datacentres, high performance computing clusters and advanced industrial simulation platforms. As governments, utilities and contractors lean ever more heavily on AI driven modelling, predictive maintenance and digital twins, the performance of memory subsystems is becoming as strategically important as power supply or cooling design.

By moving first into mass production, Samsung positions itself at the heart of the next generation AI infrastructure cycle. That matters not only to chip designers and GPU manufacturers, but to investors, policymakers and contractors who are grappling with unprecedented demand for AI ready facilities across Europe, North America, the Middle East and Asia.

HBM4 For Infrastructure And Construction

High Bandwidth Memory is a specialised type of DRAM designed for extremely high data throughput with lower power consumption per bit transferred. It is typically stacked vertically using through silicon via technology and placed close to GPUs and AI accelerators. The result is dramatically higher memory bandwidth compared to conventional DDR memory.

For the construction and infrastructure sectors, that technical detail has practical consequences. AI workloads used for traffic modelling, climate resilience simulations, materials science, autonomous vehicle training and smart city analytics rely on vast data sets and complex parallel processing. When memory becomes a bottleneck, project timelines and innovation cycles slow down.

Industry research from organisations such as the International Energy Agency and McKinsey has highlighted the exponential growth in AI compute demand, with datacentre electricity consumption projected to rise sharply through the end of the decade. As AI models scale in size and complexity, memory bandwidth becomes a limiting factor. HBM4, with its higher throughput and improved efficiency, directly addresses that constraint.

Samsung’s HBM4 delivers a processing speed of 11.7 gigabits per second, compared to the 8Gbps industry standard for earlier HBM generations. That represents an increase of roughly 46 percent. Performance can be enhanced up to 13Gbps in certain configurations, providing additional headroom as AI models continue to expand.

In real world terms, that means GPUs can be fed data more quickly and consistently, improving utilisation rates and reducing idle cycles. For datacentre operators, better GPU throughput translates into higher productivity per rack and, ultimately, improved return on capital invested in AI hardware.

Performance Gains And The Battle Against Bottlenecks

Memory bandwidth per single stack has increased significantly compared to the previous HBM3E generation, reaching up to 3.3 terabytes per second. Samsung reports this represents a 2.7 times increase over HBM3E.

That jump is particularly relevant for hyperscalers and specialist AI infrastructure providers building new facilities in markets such as Saudi Arabia, the United States and Singapore. As governments invest in sovereign AI capability and digital infrastructure, the ability to deploy higher performance memory modules at scale becomes a strategic differentiator.

Samsung has achieved these gains by leveraging its sixth generation 10 nanometre class DRAM process, known as 1c, alongside advanced logic processes. According to Sang Joon Hwang, Executive Vice President and Head of Memory Development at Samsung Electronics: “Instead of taking the conventional path of utilizing existing proven designs, Samsung took the leap and adopted the most advanced nodes like the 1c DRAM and 4nm logic process for HBM4. By leveraging our process competitiveness and design optimization, we are able to secure substantial performance headroom, enabling us to satisfy our customers’ escalating demands for higher performance, when they need them.”

From an infrastructure perspective, that headroom is not just about speed. It allows system architects to design platforms with longer performance lifecycles, reducing the frequency of major hardware refresh cycles. For publicly funded research centres and national AI initiatives, that can translate into more predictable capital planning.

Energy Efficiency And Thermal Management In The AI Era

Datacentres are now a core part of national infrastructure. Yet they face mounting scrutiny over energy consumption, carbon emissions and water use. The integration of higher performance memory modules must therefore be balanced against power and thermal constraints.

Samsung states that HBM4 achieves a 40 percent improvement in power efficiency compared to HBM3E, using low voltage through silicon via technology and power distribution network optimisation. Thermal resistance has been enhanced by 10 percent, and heat dissipation by 30 percent.

Those figures are particularly relevant as the number of data input and output pins doubles from 1,024 to 2,048. Without careful design, that increase could have driven up power consumption and heat generation substantially.

Improved energy efficiency at the memory level cascades through the entire facility. Lower power draw per GPU can reduce cooling loads, enabling more compact rack designs or lower overall energy intensity. In regions such as the European Union, where regulatory frameworks such as the Energy Efficiency Directive and taxonomy regulations are tightening, incremental gains in component efficiency can have material impact on compliance and operational costs.

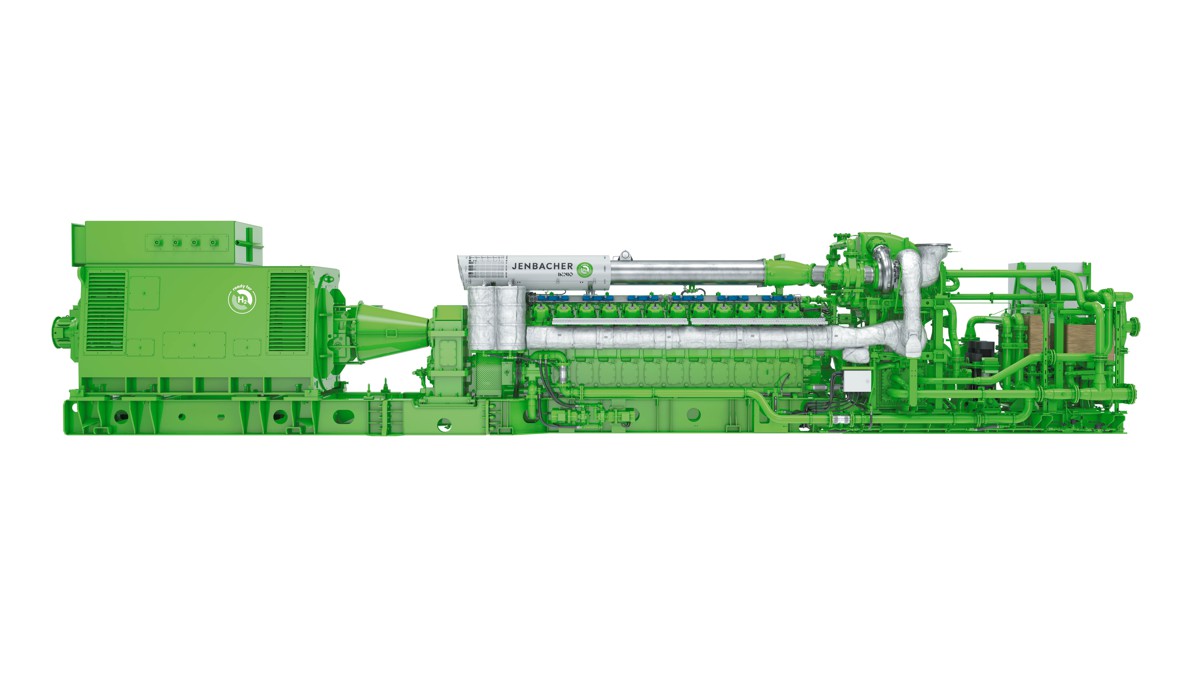

For contractors building AI ready campuses, these technical improvements influence mechanical and electrical design specifications, from chilled water systems to backup power sizing. The knock on effect is felt across the supply chain, including switchgear manufacturers, cable suppliers and cooling technology providers.

Capacity Scaling And The Next Phase Of AI Growth

Samsung is offering HBM4 in 12 layer stacks with capacities ranging from 24GB to 36GB. It has also outlined plans to utilise 16 layer stacking technology, expanding capacity up to 48GB in line with future customer timelines.

The move towards higher capacity stacks aligns with trends observed across the AI industry. Training large language models, advanced computer vision systems and industrial simulation platforms demands ever larger memory pools per accelerator. Increasing capacity per stack can simplify board layouts and reduce the number of discrete components required.

That simplification has implications for hardware manufacturers designing AI servers and for datacentre operators optimising rack density. Fewer components can mean lower failure rates, simplified maintenance regimes and potentially improved reliability metrics across large scale deployments.

Samsung anticipates that its HBM sales will more than triple in 2026 compared to 2025 and is expanding production capacity accordingly. It has also indicated that sampling for HBM4E is expected to begin in the second half of 2026, with custom HBM samples reaching customers in 2027.

For infrastructure investors, those forward looking statements provide visibility into the next wave of AI hardware upgrades. Capital expenditure cycles in datacentres often span several years. Knowing that higher performance memory variants are already on the roadmap allows operators to align facility expansion plans with component availability.

Manufacturing Scale And Supply Chain Resilience

Beyond performance metrics, Samsung’s announcement highlights its manufacturing scale and integration between its foundry and memory businesses. It references a tightly integrated design technology co optimisation approach aimed at securing quality and yield.

In a post pandemic environment where semiconductor shortages disrupted automotive production lines and delayed infrastructure projects, supply chain resilience is no longer an afterthought. Governments in the United States, the European Union and parts of Asia have introduced incentives to strengthen domestic semiconductor manufacturing capacity.

Samsung’s early mass production of HBM4 and its investment in production capacity expansion send a signal to the market that supply constraints may ease for this specific segment. That is significant for GPU manufacturers and hyperscalers who have faced tight allocation of advanced memory in recent years.

For construction professionals delivering new datacentre campuses, predictable component supply reduces the risk of project delays caused by hardware shortages. For policymakers, it reinforces the importance of semiconductor ecosystems as critical infrastructure in their own right.

Implications For The Broader Industrial Technology Landscape

While much of the discussion around HBM4 centres on generative AI, its impact extends into industrial automation, digital twins and advanced engineering. High fidelity simulation of infrastructure projects, from bridge load modelling to flood risk analysis, depends on high performance computing resources.

As construction firms adopt AI driven design optimisation and autonomous equipment technologies, the demand for compute power will not remain confined to hyperscale datacentres. Edge computing nodes at ports, rail hubs and smart motorways will also require efficient, high bandwidth memory solutions.

In that sense, HBM4 represents another building block in the digital transformation of physical infrastructure. Faster, more efficient memory modules may not grab headlines in the same way as a new motorway or rail line, yet they underpin the analytics and automation that increasingly define how those assets are planned, built and managed.

Samsung’s early leadership in HBM4 therefore resonates beyond the semiconductor industry. It touches on energy policy, construction strategy, digital sovereignty and the economics of AI deployment at scale. As AI workloads continue to grow and infrastructure investors scrutinise both performance and sustainability metrics, memory technology will remain a quiet but decisive factor in shaping the next chapter of global infrastructure development.