Arrow Electronics announces Intelligent Vision Ecosystem

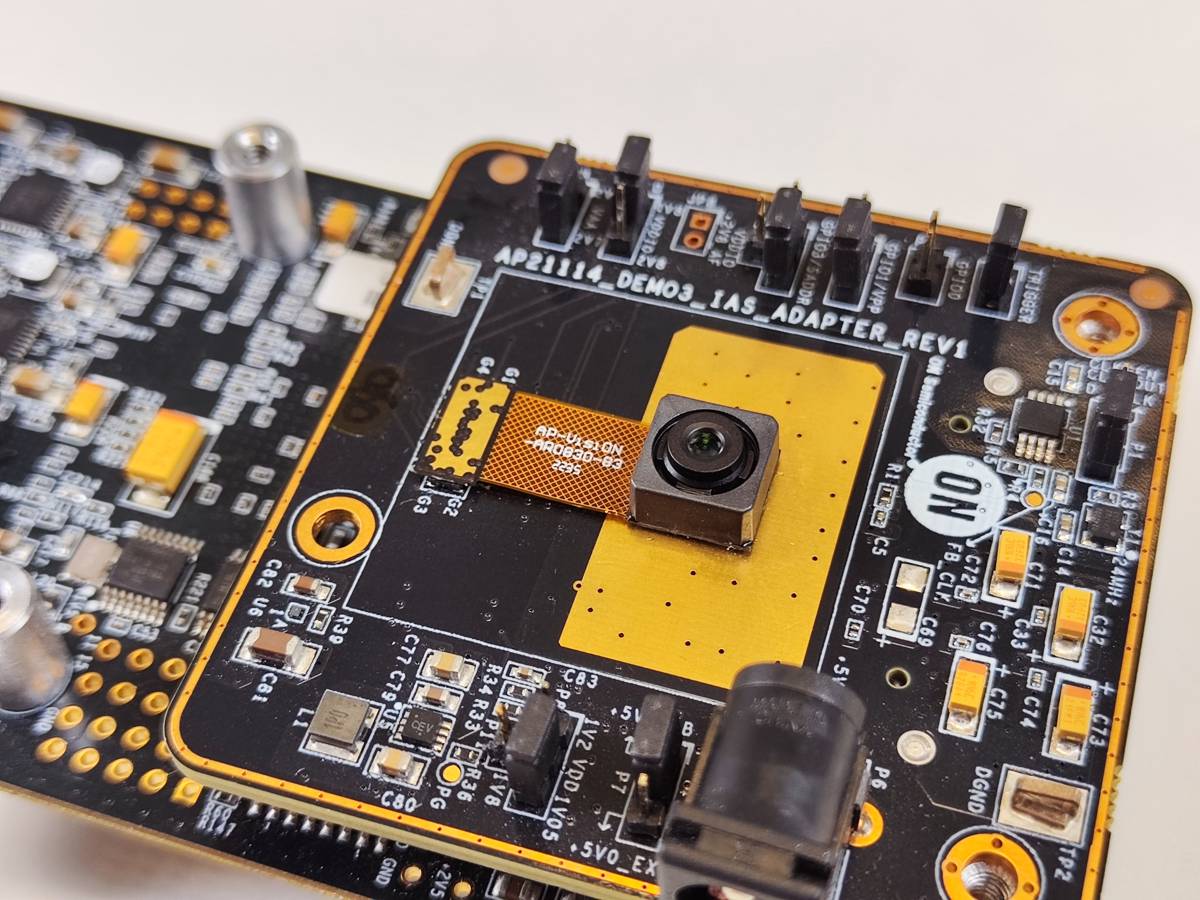

Arrow Electronics, Inc. is utilizing the onsemi™ Imager Access System (IAS) module standard for developing intelligent vision solutions for use in robotics, machine vision, commercial cameras and other uses.

The solution reduces the design complexities that are common with designing a product that utilizes image sensors. Part of that complexity is there is no standardization of the hardware interfaces of the different technology blocks. This is where the onsemi™ IAS module standard comes in and is adopted throughout the ecosystem.

Working with Appletec, Arrow developed the newest IAS module, AP-VISION-AR0830-83, that utilizes the latest generation of onsemi image sensors.

“The onsemi Hyperlux™ LP family of sensors set a new industry benchmark for ultra-low power sensor design. Combined with a small form factor, purpose-oriented features and best-in-class imaging, Hyperlux LP will be a fixture for smart home, office, and robotics for years to come,” said Stephen Harris, senior director of marketing for onsemi’s Industrial and Commercial Sensing Division. “onsemi is now able to bring the newest high-performance, feature-rich 4K sensor in the Hyperlux family, AR0830, to market with Arrow’s IAS module, allowing our customers to reduce camera development efforts significantly with best-in-class module design.”

This new module joins the existing portfolio of IAS modules offered by Arrow and Appletec.

Arrow worked with its company, eInfochips, and onsemi to develop drivers that enable the Appletec IAS modules to work with leading embedded processors.

“eInfochips has extensive experience in developing end-to-end vision solutions. This includes hardware design, image sensor integration and tuning, image processing, image driver development, low latency streaming and AI Inferencing on edge/cloud,” said Gaurav Patel, vice president and general manager of product engineering services for eInfochips. “Companies rely on eInfochips to deliver innovative vision solutions and accelerate and de-risk design cycles.”